Chair of Computer Science 3 – Computer Architecture

Overview

The Chair of Computer Science 3 (Computer Architecture) has a long tradition with over 50 years research on parallel computing. Message- and memory-coupled parallel computers like EGPA, DIRMU and MEMSY, developed under the founder of the chair, Prof. Wolfgang Händler, have gained large reputation in the scientific community in the past. This has found its continuation with a focus on research about fault-tolerance architectures under his successor, Prof. Mario Dal Cin.

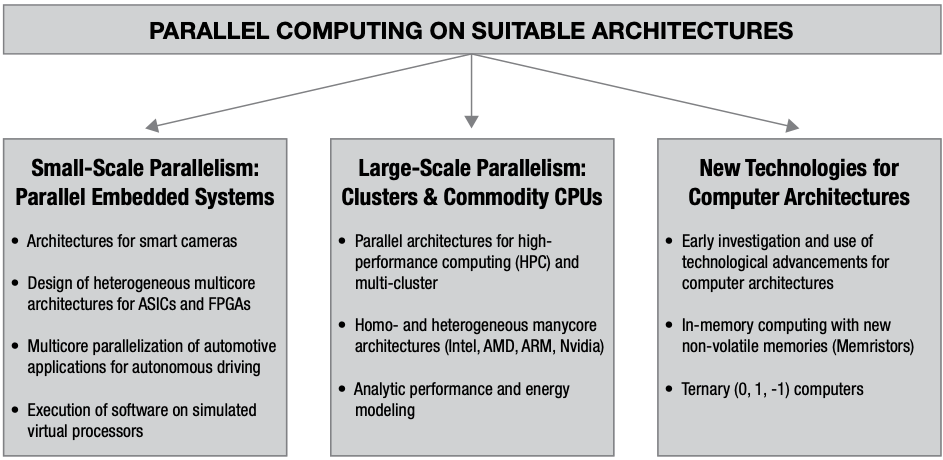

Over the decades parallel computing has changed and the chair’s research under the lead of Prof. Dietmar Fey faces now new challenges like heterogeneous computing and the next to expect important thing in computer architecture research, namely near-memory and in-memory computing.

This is reflected in the daily chair’s research work which is focused on three pillars: design of application specific architectures and modelling for embedded HPC, performance modelling for heterogeneous HPC, and unconventional computing using memristor technology.

In projects funded by Bavarian Research Foundation, the German Ministry for Research and Education, and the German Research Foundation as well as in direct third-party funding research projects by industry the chair researches on future computer architectures in cars for autonomous driving, specific accelerator cores for AI, future ternary processor architectures using multi-level cell memristive devices, and performance modelling and engineering of current HPC and embedded processors and GPUs from Intel, AMD, ARM, Nvidia and own designs on RISC-V base.

People

Prof. Dr. Dietmar Fey

Dr. Marc Reichenbach

Dr. Alexander Ditter

Dr. Johannes Hofmann

Research topics

- Fusion of High Performance and Cloud Computing

- Performance Engineering: Bringing high performance to anything from GPUs to embedded devices

- Modeling

- Analytic performance, power, and energy models for modern server processors

- Performance Modeling of programmable embedded systems utilizing emulation and mechanistic performance models

- Modeling of dedicated hardware accelerators such as programmable logic (e.g. FPGAs) and ASICs for special application fields e.g. AI

- Modeling of emerging technologies (memristors, near-/in-memory computing)

Research projects

KI-Flex

The joint KI-FLEX project, which runs through August 2022, is funded by the German Federal Ministry of Education and Research (BMBF) within the framework of the guidelines on promoting research initiatives in the field of “AI-based electronic solutions for safe autonomous driving (AI element: autonomous driving).” The goal of this project is the development of powerful and energy-efficient hardware platforms with a dedicated software framework for the application field of autonomous driving. The “KI-FLEX”-Platform should be able to collect process and consolidate laser, camera and radar data utilizing methods of artificial intelligence. Our part of this project is the transparent usage of embedded FPGAs in the “KI-FLEX”-Platform including the performance gain by using these reconfigurable logic devices.

Project Leader: Fraunhofer IIS

Leader at our Location: Reichenbach / Fey

IMBRA

The aim of the project IMBRA, which is funded for 3 years by DFG, is to use memristor technology in modern computer architectures; especially for the integration of memristive devices in a CPU for embedded applications. For a further reduction of the energy consumption also the ability of storing more than one bit in a single memristor cell can be used to enable the realization of tenary logic, which requires multi-bit-storage in a memristive register. Tenary logic will result in a redundant number representation, which allows to execute an adding during a constant time independent of the word length. This also results in a decreased power consumption. The computer architectures will be realized as a prototype IC and performance predictions will be made for future CPUs.

Project Leader: Our Chair and LTE

Leader at our Location: Fey / Reichenbach

LO3-ML – Sprunginnovation

The goal of this project is the development of an energy efficient hardware architecture for the detection of ventricular fibrillation utilizing methods of artificial intelligence, e.g. by deep using neuronal networks. To increase performance and safe power, the hardware architecture contains non-volatile RAMs (e.g. memristors) to store the weights of the neuronal networks. Furthermore, trough quantization and efficient arithmetic circuits a further performance gain will be available. The architecture will be evaluated regarding power, performance and energy efficiency. Initially, the project is funded as part of a competition for 1 year – After a review phase, the best project ideas get funding for a complete chip development.

Project Leader: Our Chair

Leader at our Location: Reichenbach / Fey

ECAS (Embedded Computing for Advanced Signal Processing in Cars)

The ECAS project is funded by the Bavarian Research Foundation (BFS). Its aim is to research architectures for high performance computing in cars with focus on complex signal processing algorithms that could not be previously implemented in embedded systems due to missing computational performance. In cooperation with Infineon AG and XKrug GmbH a prototype for future computing platforms will be developed that shows the combination of realtime processors with accelerator hardware like GPUs and FPGAs.

Project Leader: Fey

Selected publications

- Rachuj, Sebastian ; Reichenbach, Marc ; Fey, Dietmar: A Generic Functional Simulation of Heterogeneous Systems. In: Schoeberl, Martin ; Hochberger, Christian ; Uhrig, Sascha ; Brehm, Jürgen ; Pionteck, Thilo (Hrsg.) : Proceedings (Architecture of Computing Systems – ARCS 2019, Copenhagen, Denmark, 20.-24.05.2019).

- Fritscher, J. Knödtel, M. Reichenbach and D. Fey, “Simulating Memristive Systems in Mixed-Signal Mode using Commercial Design Tools,” 2019 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Genoa, Italy, 2019, pp. 225-228.

- Bauer, Wolfgang ; Holzinger, Philipp ; Rachuj, Sebastian ; Häublein, Konrad ; Reichenbach, Marc ; Fey, Dietmar: Evaluating HSA-Compatible Heterogeneous Systems for ADAS Applications. In: Trinitis, Carsten ; Pionteck, Thilo (Hrsg.) : Workshop Proceedings (ARCS 2019: 32nd International Conference on Architecture of Computing Systems, Copenhagen, Denmark, 20.-24.05.2019).

- Holzinger, Philipp ; Reichenbach, Marc ; Fey, Dietmar: A New Generic HLS Approach for Heterogeneous Computing: On the Feasibility of High-Level Synthesis in HSA-Compatible Systems.In: Mudge, Trevor ; Pnevmatikatos, Dionisios N. (Hrsg.) : SAMOS XVIII: 2018 International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation

- Rachuj, Sebastian ; Herglotz, Christian ; Reichenbach, Marc ; Kaup, André ; Fey, Dietmar: A Hybrid Approach for Runtime Analysis Using a Cycle and Instruction Accurate Model. In: Berekovic, M. ; Buchty, R. ; Hamann, H. ; Koch, D. ; Pionteck, T. (Hrsg.) : Architecture of Computing Systems – ARCS 2018

- Reichenbach, Marc ; Liebischer, Lukas ; Vaas, Steffen ; Fey, Dietmar: Comparison of Lane Detection Algorithms for ADAS using Embedded Hardware Architectures. In: IEEE (Hrsg.) : Proceedings of 2018 Conference on Design and Architectures for Signal and Image Processing (DASIP)

- Vaas, Steffen ; Ulbrich, Peter ; Reichenbach, Marc ; Fey, Dietmar: The Best of Both: High-performance and Deterministic Real-Time Executive by Application-Specific Multi-Core SoCs. In: HEART (Veranst.): Proceedings of the Conference on Design and Architectures for Signal and Image Processing (DASIP ’17)

- Ditter A., Tielemann M., Fey D.: Bridging the gap between high-performance, cloud and service-oriented computing, 4th IEEE International Workshops on Foundations and Applications of Self* Systems, FAS*W 2019 (Umea, SWE, 06/16/19 – 06/20/19), DOI: 10.1109/FAS-W.2019.00029

- Hofmann, G. Hager, D. Fey: On the accuracy and usefulness of analytic energy models for contemporary multicore processors.High Performance Computing: 33rd International Conference, ISC High Performance 2018, Frankfurt, Germany, June 24-28, 2018, Proceedings. DOI: 10.1007/978-3-319-92040-5_2Preprint: arXiv:1803.01618

- Hofmann, G. Hager, G. Wellein, D. Fey: An analysis of core- and chip-level architectural features in four generations of Intel server processors.High Performance Computing: 32nd International Conference, ISC High Performance 2017, Frankfurt, Germany, June 18-22, 2017, Proceedings. DOI: 10.1007/978-3-319-58667-0_16Preprint: arXiv:1702.07554

- Hofmann, D. Fey, M. Riedmann, J. Eitzinger, G. Hager, and G. Wellein: Performance analysis of the Kahan-enhanced scalar product on current multi- and manycore processors.Concurrency and Computation: Practice and Experience, ISSN: 1532-0634. DOI: 10.1002/cpe.3921Preprint: arXiv:1604.01890

- Hofmann and D. Fey: An ECM-based energy-efficiency optimization approach for bandwidth-limited streaming kernels on recent Intel Xeon processors. 4th International Workshop on Energy Efficient Supercomputing, Salt Lake City, UT, USA, November 14, 2016, Proceedings. DOI: 10.1109/E2SC.2016.16 Preprint: arXiv:1609.03347

- J. Hofmann, D. Fey, J. Eitzinger, G. Hager, and G. Wellein: Analysis of Intel’s Haswell Microarchitecture Using the ECM Model and Microbenchmarks. Architecture of Computing Systems – ARCS 2016: 29th International Conference, Nuremberg, Germany, April 4-7, 2016, Proceedings. DOI: 10.1007/978-3-319-30695-7_16 Preprint: arXiv:1511.03639